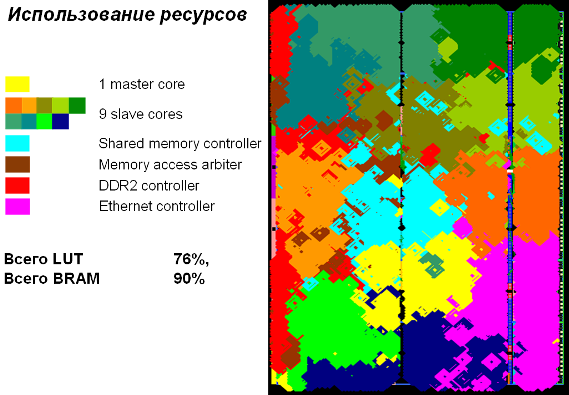

A new smart memory controller with DMA support has been developed

- Details

- Published: Friday, 10 October 2014 21:08

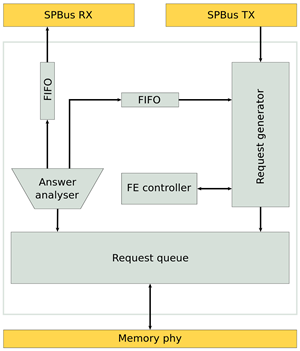

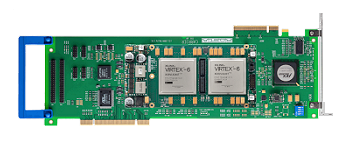

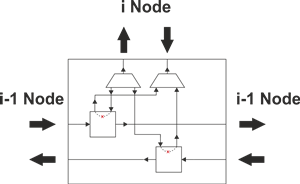

A new version of the smart memory controller has been developed and tested. Now the controller maintains block data transfers - usually this calls ‘DMA’ - a system, enabling to copy data from one memory area to another without involving processing cores. The usage of the mechanism allows to increase performance of intensive data exchange tasks in several times. There is a basic set of "real" atomic operations in the controller, for instance, atomic increment is supported.