IP-blocks

MALT design center develops digital and analog IPs according to customer requirements. The company’s portfolio includes both Soft IPs and Hard IPs for design of modern VLSI and SoC. IPs are developed for specific technological process of a particular factory according to the requirement specification. Occasionally, we have to develop interface blocks for VLSI integration, when using third-party manufacturers’ IPs.

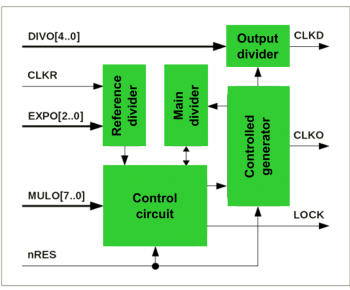

FDPLL

A programmable fully digital PLL (FDPLL) designed to lock to an incoming clock source and produce an output clock. It is ideal as a clock generator for digital designs, but not intended for analog blocks like ADC / DAC or SERDES clocking. This digital PLL has ultra-low area and low implementation charges due to predictable digital design.

TECHNICAL SPECIFICATION 28nm

| Parameter | Unit | Min | Typ | Max | Comment |

|---|---|---|---|---|---|

| Reference frequency | MHz | 0.8 | 1000 | ||

| Output frequency | MHz | 200 | 2000 | ||

| Auxiliary frequency | MHz | 3.125 | 1000 | ||

| Period jitter | % | < | 2 | CLKO=1000 МГц | |

| Duty cycle | % | 45 | 50 | 55 | |

| Power | mW | 5 | CLKO=1000 МГц | ||

| Operational voltage | V | 0.8 | 0.9 | 1.0 | Digital only |

| Total area | mm2 | 0.012 | |||

| Operational temp | C | 0 | 70 | 85 |

TECHNICAL SPECIFICATION 16nm

| Parameter | Unit | Min | Typ | Max | Comment |

|---|---|---|---|---|---|

| Reference frequency | MHz | 1.2 | 3000 | ||

| Output frequency | MHz | 300 | 3000 | ||

| Auxiliary frequency | MHz | 1500 | |||

| Period jitter | % | <2 | CLKO=1000 МГц | ||

| Duty cycle | % | 45 | 50 | 55 | |

| Power | mW | 5 | CLKO=1000 МГц | ||

| Operational voltage | V | 0.72 | 0.8 | 0.99 | Digital only |

| Total area | mm2 | 0.0036 | |||

| Operational temp | C | -40 | 85 | 125 |

Description

In the capture mode PLL provides periodic signal on CLKO output with period equal to CLKR inputs period multiplied by MULO:EXPO value. Where MULO: EXPO is a denormalized floating-point number, MULO is an 8-bit mantissa, EXPO is a 3-bit exponent. Multiplication coefficient is calculated as follows: the EXPO exponent code [2..0] is interpreted as integer from 0 to 7, which determines the position of the binary point inside the MULO mantissa [7..0]. EXPO numerical value is the number of the MULO digit, followed by a binary dot dividing MULO into integer and fractional parts (the size of the fractional part). For EXPO = 0, the fractional part is absent, and the entire integer part is in MULO [7..0]. For EXPO = 7, the integer part is in MULO [7], fractional in MULO [6..0]. In addition to the main output of the generator, the module has an auxiliary output CLKD, the frequency of which is obtained by dividing the main frequency by a factor of 2*DIVO [4..0].

Table. Pin list

| Signal | Direction | Comment |

|---|---|---|

| nRES | input | Asynchronous Reset (Active Low) |

| CLKR | input | Reference frequency |

| MULO[7..0] | input | Mantissa of the multiplication coefficient |

| EXPO[2..0] | input | The exponent of the multiplication factor |

| DIVO[4..0] | input | Post-divider ratio |

| CLKO | output | Output frequency |

| CLKD | output | Auxiliary frequency after the divider |

| LOCK | output | Capture indication (Active High) |

| FDPLL 28nm Datasheet |

| FDPLL 16nm Datasheet |

FDPLL 28 nm, 16 nm is available on design-reuse.com.

IP PORTFOLIO INCLUDES:

- IPs for modern crypto accelerators on such standards as DES, AES, SHA, etc.

- IPs for voltage references and thermal sensors (LDO, t).

- IPs for high-speed transmission channels (LVDS, SSTL).

- IPs for data serialization and clock recovery (PMA).

- IPs for scrambling and data encryption (PCS 8/10, 64/66).

- IPs for high-speed serial interfaces (SERDES).

- IPs for Ethernet logical layer 10/100/1G/10G (Ethernet MAC).

- IPs for Ethernet physical layer 10/100/1G/10G (Ethernet PHY).

- IPs for DDR 1/2/3/4 logical layer (DDR logic).

- IPs for memory controllers RLDRAM (logic).

- IPs for high-speed static memory controllers (QDR SRAM logic).

- IPs for periphery (I2C, I2S, SPI, UART, etc.).

We implement after-sale support in terms of optimization, interfaces, compatibility and IP integration in SoC. We provide software updates for our IPs. We guarantee information security and legal transparency for the supplied IPs.

PLEASE FEEL FREE TO CONTACT US TO GET MORE INFORMATION ABOUT MALT FEATURES!