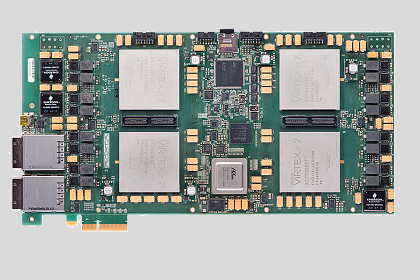

96-core MALT prototype with mixed architecture on FPGA Xilinx Virtex7 has been built

- Details

- Published: Thursday, 24 March 2016 20:22

|

Photo: maltsystem.com |

96-core MALT prototype with mixed architecture on FPGA Xilinx Virtex7 has been built. The prototype includes 3 general-purpose RISC cores and 96 SIMD processing elements. 512 kb BRAM is used as external memory in the prototype to provide minimum access latency. The operation frequency of general-purpose RISC cores - 100 MHz, SIMD processing elements - 80 MHz, on-chip bus - 150 MHz. Therefore, it’s safe to say that “in silicon” such design will be able to operate at frequencies up to 1 GHz.