210-core processor on FPGA Xilinx Virtex7 has been built

- Details

- Published: Sunday, 28 December 2014 17:56

|

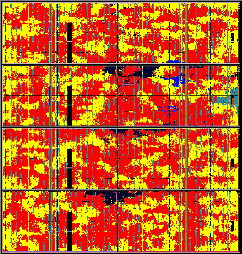

210-core processor scheme |

Recently we’ve finished the assembling and debugging of a new monster - 210-core processor prototype on FPGA Xilinx Virtex7 2000T. This is the biggest chip in the 7th generation of Xilinx FPGA. And our MALT system is the largest array of independent 32-bit RISC cores prototyped on a single FPGA known today. This prototype will be used for debugging real tasks of the general resource controller, primarily, debugging the smart memory controller with hundreds of calls from multiple cores. Also, such system will enable to study on-chip bus behavior during peak loads at various configurations (number of core chains and their length).

- Technical characteristics of current processor:

- Core clock frequency - 75 MHz.

- Local data memory size - 4 Kb/core.

- Local command cache size - 4 Kb/core.

- Internal bus bit depth - 128 b.

- Internal bus clock frequency - 125 MHz.

Up to 1 GB RLDRAMIII may be used as external memory. The amount of available RAM may be increased by using host computer memory with PCIe connection. The maximum memory size at such configuration - 256 GB.

The current processor version is implemented on Rosta-RC47 hardware platform built on FPGA Xilinx Virtex-7 2000T. The project utilizes 59% LUT and 95% BRAM.