Процессоры MALT презентовали для кластера "Техноюнити"

- Информация о материале

- Опубликовано: 31.07.2018, 12:14

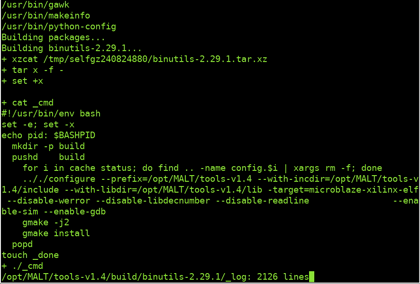

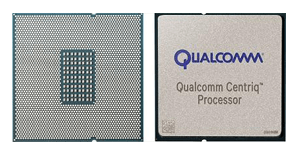

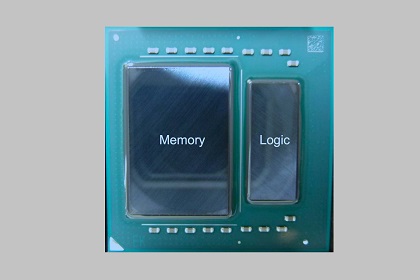

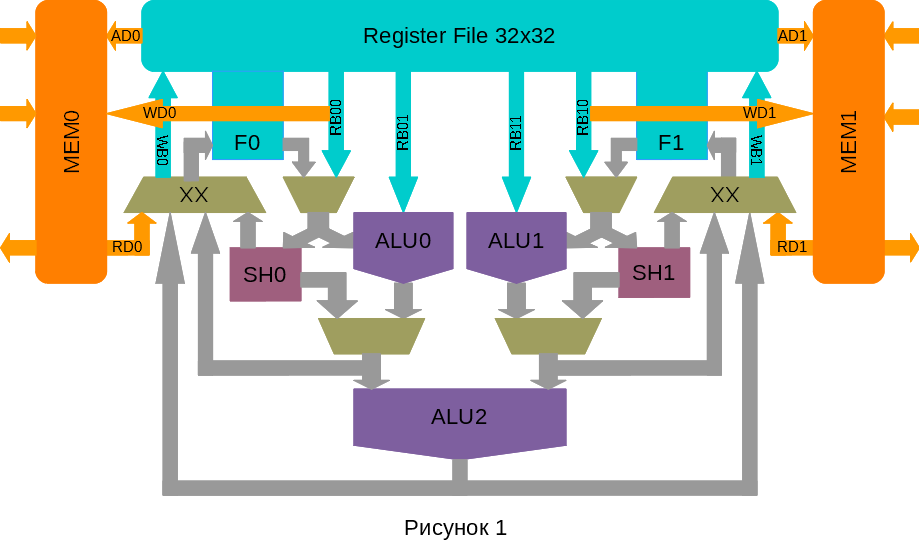

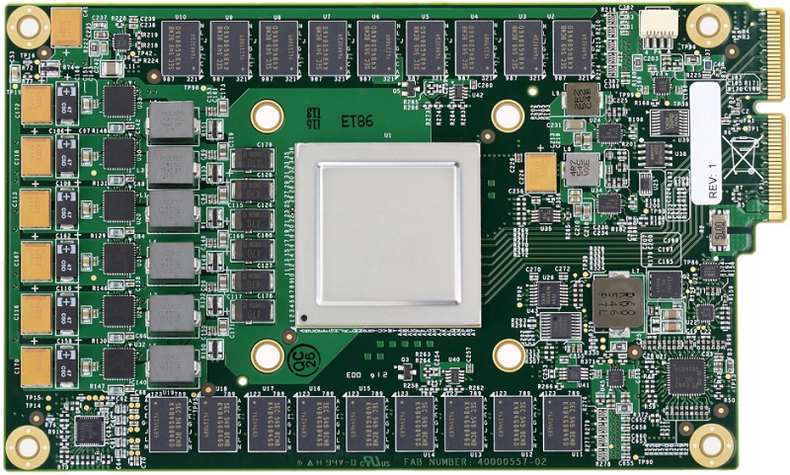

Наши партнёры ООО «ЦИФ МГУ имени М. В. Ломоносова» - участник инновационного территориального кластера «Зеленоград» (кластер TechnoUnity), обособленного научно-индустриального района Москвы со специализацией в области микроэлектроники и высокотехнологичного бизнеса. На встрече с руководством кластера была показана презентация процессоров MALT.