Ассоциативная память на ПЛИС, как сделать?

- Информация о материале

- Опубликовано: 11.01.2022, 10:00

Разработка проблемно-ориентированных процессоров - это всегда поиск оптимальных по энергетике и площади специализированных функциональных блоков. Здесь нет готовых решений, нужно пробовать, разрабатывать, имплементировать в дизайн, сравнивать и так много раз, пока мы не найдем лучшее, а дальше нужно выжать из лучшего все соки путем трудоемкой ручной оптимизации. Однако, прежде чем выжимать, необходим верный концепт, обычно он делается на ПЛИС. Обычно он не демонстрирует топовых характеристик, но позволяет сравнить разные подходы к решению конкретной задачи, выбрать тот подход, который далее подвергнется глубокой доводке. Зачем? Почему бы не купить сразу крутое готовое решение и не "мучиться выбором"? Потому, что в этом случае вы поймете, что оптимизировали не то, только когда в работу будет вложено слишком много сил или не поймете вообще, как и оставшись в плену рекламных брошюр. В общем, перейдем к делу.

Сегодня мы хотим поделиться с вами статьей для хабра нашего ведущего RTL–разработчика, в которой рассказывается о практической реализации блока ассоциативной памяти СAM (content-addressable memory) на ПЛИС. Никаких секретов, возможно наше решение будет полезно и вам. CAM - это такой вид памяти, в котором адресация осуществляется на основе данных, а не их адреса (как обычно), чем обеспечивается ускорение поиска необходимых записей в некоторых режимах работы, а в некоторых замедляется. Итак, перед нами стояла следующая задача: требовалось сделать небольшой CAM с шириной слова 8-64 бит и глубиной 16-1024 слов, с бинарным поиском и частотой выше 100 МГц.

|

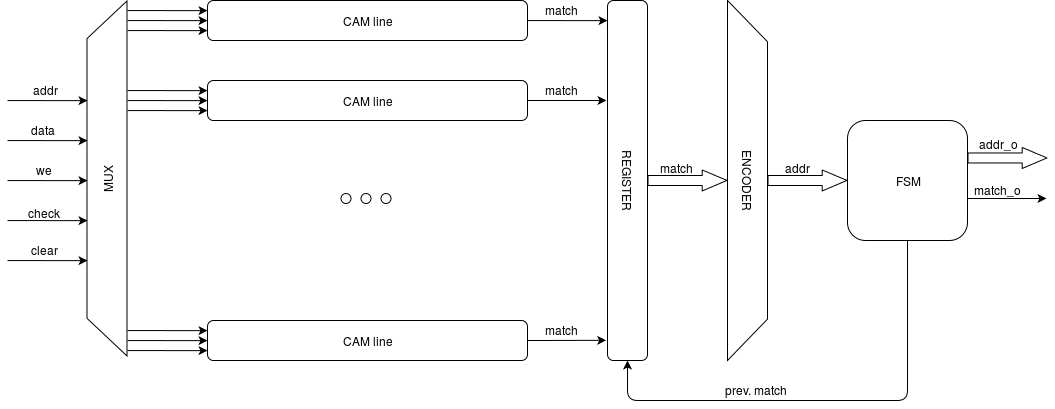

| Структура CAM |

|

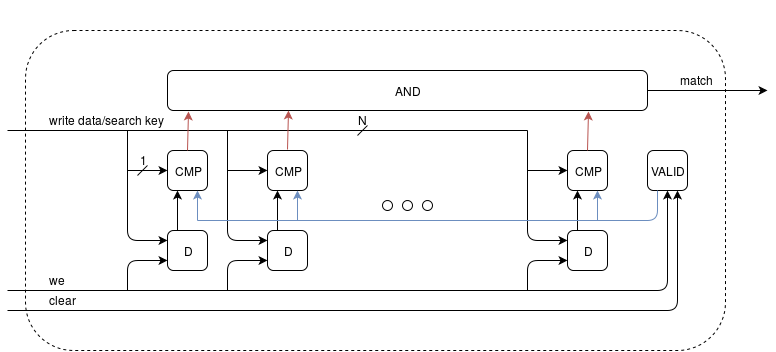

| Структура одной линейки CAM |

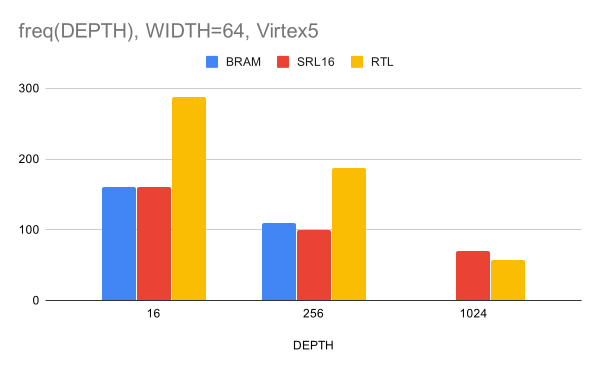

На рисунках выше показана структура блока CAM, а также детализированная структура одной линейки CAM. Реализованный блок CAM состоит из нескольких линек CAM; входного адресного мультиплексора (MUX); регистра, сохраняющего значения флагов совпадения match (REGISTER); дешифратора, преобразующего шину совпадений в младший из найденных адрес совпадений (ENCODER) и управляющего конечного автомата (FSM). Полученный дизайн позволяет на 7-м семействе ПЛИС Xilinx получать достаточно большие CAM с частотой выше 125 МГц. Результат сравнения с CAM на BRAM и на SRL16 показал, что реализованный блок обеспечивает частоту большую, чем у остальных реализаций (исключение составляет реализация для глубины в 1024 слов и ширины данных 64 бит).

|

| Зависимость частоты после XST от глубины CAM для ширины шины данных 64 бита. |

Резюме: CAM на ПЛИС - это не так уж и сложно. Если в вашем дизайне планируется ассоциативная память, не бегите реализовывать ее программно, попробуйте чуть более "железный" CAM и сравните! Надеемся, что наша статья вас заинтересует и будет полезной, а мы будем стараться чаще делиться практическим опытом.

P.S. Статья написана еще в 2019-том, извиняемся что пост подошел только сейчас, текущая работа в компании настолько интенсивна, что до новостей время дошло только сейчас :(