# SOVIET ADVANCED TECHNOLOGY: THE CASE OF HIGH-PERFORMANCE COMPUTING

by

Peter Wolcott

Copyright © Peter Wolcott 1993

A Dissertation Submitted to the

## COMMITTEE ON BUSINESS ADMINISTRATION

In Partial Fulfillment of the Requirements For the Degree of

DOCTOR OF PHILOSOPHY

In the Graduate College

THE UNIVERSITY OF ARIZONA

1993

#### STATEMENT BY AUTHOR

This dissertation has been submitted in partial fulfillment of requirements for an advanced degree at The University of Arizona and is deposited in the University Library to be made available to borrowers under rules of the Library.

Brief quotations from this dissertation are allowable without special permission, provided that accurate acknowledgment of source is made. Requests for permission for extended quotation from or reproduction of this manuscript in whole or in part may be granted by the copyright holder.

SIGNED: \_

#### ACKNOWLEDGEMENTS

This work more than a piece of scholarly research. It is a tapestry weaving together not only data and analysis, but also the lives and experiences of all those who have had a part in it, or whose work is described. I value the human element embodied in it highly.

I have been privileged to work in The Mosaic Group. This study would have been much more difficult had I not had access to the expertise of the members of the group, the data they have collected, and the research tools they have built. Professor and Mrs. Seymour Goodman, Professor Tom Jarmoszko, Dr. Kevin Lynch, Professor William Mc-Henry, Dr. Ross Stapleton, Dr. Joel Snyder and many current and former Mosaic members have given me greatly valued information, criticism, advice, and friendship across many years and many countries.

Each of my committee members, Joey George, Seymour Goodman, William Mc-Henry, and Ram Nidumolu, made distinct contributions to this dissertation. It would have been a much weaker study without the contribution of each.

Without the role played by Sy Goodman, this dissertation would not have been written. Since 1985 he has provided the opportunity, support, guidance, criticism, companionship, and encouragement necessary to carry this work to completion.

This dissertation would have been impossible to write without the assistance of many scientists and engineers who have been intimately involved with Soviet computing, and the development of high-performance computing systems. The friendships and professional relationships I have established with them are particularly meaningful. I cannot list all those who helped me by providing information and insights here. I am, however, particularly grateful for the assistance of the following individuals: B. A. Babayan, N. Ye. Balakirev, V. S. Burtsev, M. N. Dorozhevets, O. S. Gus'kov, V. V. Ignatushchenko, I. I. Itenberg, V. P. Ivannikov, A. V. Kalyayev, Yu. V. Kapitonova, V. Ye. Kotov, A. A. Letichevskiy, V. K. Levin, I. L. Medvedev, V. S. Mikhalevich, N. N. Mirenkov, I. N. Molchanov, A. S. Nabatov, V. M. Repin, V. V. Rezanov, G. G. Ryabov, Yu. P. Selivanov, I. D. Sofronov, V. A. Torgashev, E. Kh. Tyugu, A. V. Zabrodin, A. P. Zamorin.

### **DEDICATION**

This study is dedicated to those who made it possible for me to complete it and maintain my equilibrium:

my parents, Calvin and Berit Wolcott, who have been a continuous source of love and encouragement for many years;

my wife, Ellie, who is a great joy to me, and persistently reminded me that "it's the dissertation, stupid!"<sup>1</sup> and

my daughter, Elisa, who continues to remind me how many things in life are more important than this dissertation.

<sup>&</sup>lt;sup>1</sup>With apologies to Bill Clinton and his campaign staff.

"Everything has become more difficult now, but it wasn't any easier before..."

-Soviet HPC engineer, 1991

## **TABLE OF CONTENTS**

| ABSTRA | CT             |                                                |      |

|--------|----------------|------------------------------------------------|------|

| CHAPTE | R 1. IN        | TRODUCTION                                     | 20   |

| CHAPTE | R 2. RF        | ELATED RESEARCH AND METHODOLOGY                |      |

| 2.1    | Technol        | ogical Innovation in the Soviet Union          |      |

|        | 2.1.1          | Characteristics of Soviet Science              |      |

|        | 2.1.2          | Analyses of Innovation in the Soviet Union     |      |

|        | 2.1.3          | Efforts to Reform Soviet Science               |      |

|        | 2.1.4          | The Perestroika Reforms                        |      |

| 2.2    | 2 Comput       | ting in the Soviet Union                       | 55   |

| 2.3    | 8 Western      | Literature on Technological Innovation         | 57   |

|        | 2.3.1          | Technological Paradigms and Trajectories       | 57   |

|        |                | The Innovation Process                         |      |

| 2.4    | l Organiz      | zational Development                           | 63   |

| 2.5    | Researc        | ch Questions                                   | 69   |

| 2.6    | 6 Researc      | h Methodology                                  |      |

|        | 2.6.1          | Units of Analysis                              |      |

|        | 2.6.2          | Rationale for Using the Case Study Methodology |      |

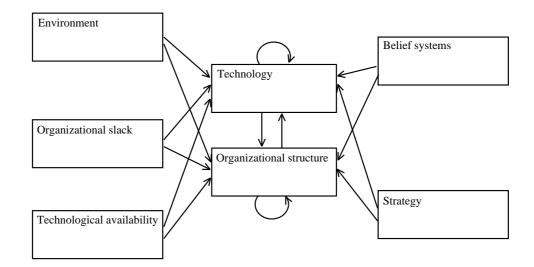

|        | 2.6.3          | Conceptual Framework                           | 77   |

|        |                | 2.6.3.1 Technology and Organizational Structur | e 78 |

|        |                | 2.6.3.2 Environment                            |      |

|        |                | 2.6.3.3 Technological Availability             | 80   |

|        |                | 2.6.3.4 Organizational Slack                   | 81   |

|        |                | 2.6.3.5 Belief Systems                         |      |

|        |                | 2.6.3.6 Strategy                               |      |

|        | 2.6.4          | Constituent Cases                              |      |

| 2.7    | <b>Data So</b> | urces and Collection, Analysis, and Validation | 86   |

|        | 2.7.1          | Sources                                        | 86   |

|         | 2.7.   | 2 Analysis     |                                                                 | 87  |

|---------|--------|----------------|-----------------------------------------------------------------|-----|

|         | 2.7.   | 3 Validation   |                                                                 | 87  |

| CHAPTER |        |                | W OF SOVIET HIGH-PERFORMANCE                                    | 89  |

| 3.1     | Introd | uction         |                                                                 | 89  |

| 3.2     | HPC E  | fforts at ITM  | IVT                                                             | 89  |

|         | 3.2.   | 1 Early Unip   | rocessors                                                       | 89  |

|         | 3.2.   | 2 ITMVT Co     | omputers of the Late 1960s and 1970s                            | 93  |

|         |        | 3.2.2.1        | BESM-10 and AS-6                                                | 93  |

|         |        | 3.2.2.2        | El'brus                                                         | 94  |

|         |        | 3.2.2.3        | SVS-1                                                           | 97  |

|         | 3.2.   | 3 ITMVT Co     | omputers of the 1980s                                           | 98  |

|         |        | 3.2.3.1        | El'brus Vector Processor                                        | 98  |

|         |        | 3.2.3.2        | Modular Pipeline Processor                                      | 100 |

|         |        | 3.2.3.3        | El'brus-B                                                       | 101 |

|         |        | 3.2.3.4        | Expansion of the El'brus Family                                 | 101 |

| 3.3     | The Pr | oliferation of | Soviet HPC Efforts (1978-1985)                                  | 103 |

|         | 3.3.   | 1 Industrial I | Projects                                                        | 104 |

|         |        | 3.3.1.1        | Attached Array Processors                                       | 104 |

|         |        | 3.3.1.2        | The PS- series                                                  | 105 |

|         |        | 3.3.1.3        | Elektronika SSBIS                                               | 108 |

|         | 3.3.   | 2 Academic     | Projects                                                        | 109 |

|         |        | 3.3.2.1        | Homogeneous Computing Systems                                   | 110 |

|         |        | 3.3.2.2        | Multiprocessor Computing Systems with Programmable Architecture | 115 |

|         |        | 3.3.2.3        | Dynamic Architecture Machines                                   | 116 |

|         |        | 3.3.2.4        | Macro-pipelined Machines                                        | 116 |

|         |        | 3.3.2.5        | The ES-270x Systems                                             | 117 |

|         |        | 3.3.2.6        | MARS                                                            | 119 |

| 3.4     | 1985-р | resent         |                                                                 | 121 |

|         | 3.4.   | 1 Policy-mal   | king Developments                                               | 121 |

|         |        | -              | ents in High-Performance Computing Systems                      |     |

|         | 3.4.3                            | Soviet Computing Associations 125                                                                                                                                                                                                                                                              |

|---------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER |                                  | STITUTE OF PRECISION MECHANICS AND COMPUTER<br>CHNOLOGY                                                                                                                                                                                                                                        |

| 4.1     | Introduc                         | tion                                                                                                                                                                                                                                                                                           |

| 4.2     | History o                        | of ITMVT Research 128                                                                                                                                                                                                                                                                          |

| 4.3     | El'brus-                         | <b>1 and El'brus-2</b>                                                                                                                                                                                                                                                                         |

|         | 4.3.2<br>4.3.3<br>4.3.4<br>4.3.5 | Requirements131Design Antecedents133Burroughs/El'brus Comparison1364.3.3.1System Organization1374.3.3.24.3.3.3Tags145147Reliability147Reliability149Performance151Differences Between the El'brus-1 and El'brus-2153                                                                           |

| 4.4     | The El'b                         | rus in the Soviet context                                                                                                                                                                                                                                                                      |

|         | 4.4.2<br>4.4.3<br>4.4.4<br>4.4.5 | The Long Road from Conception to Production154The Role of the El'brus in the Soviet Computer Industry157The El'brus Component Base160Peripheral Storage164Relationship with Factories165ITMVT Structure167                                                                                     |

| 4.5     | El'brus-                         | <b>3</b> 170                                                                                                                                                                                                                                                                                   |

|         | 4.5.2<br>4.5.3<br>4.5.4          | El'brus-3 Origins       170         System Organization       173         CPU       175         Influences on El'brus-3 Design       176         Comparison of El'brus-3 with Western VLIW Machines       178         4.5.5.1       Scheduling       178         4.5.5.2       Loops       179 |

|         |                                  | 1.5.5.2 Loops                                                                                                                                                                                                                                                                                  |

|         |           | 4.5.5.3 Instructions                               |

|---------|-----------|----------------------------------------------------|

|         |           | 4.5.5.4 Synchronization and Exception Handling 181 |

|         | 4.5.6     | Performance                                        |

|         | 4.5.7     | Status                                             |

| 4.6     | El'brus I | Microprocessors                                    |

|         | 4.6.1     | El'-90                                             |

|         | 4.6.2     | El'-95                                             |

| 4.7     | A Period  | of Change                                          |

|         | 4.7.1     | Demand for ITMVT Computers                         |

|         | 4.7.2     | Relationships with Suppliers 189                   |

|         | 4.7.3     | Relationships with the Factories                   |

|         | 4.7.4     | Relationship with the Ministry 192                 |

| 4.8     | The Resp  | ponse to Change                                    |

|         | 4.8.1     | Changes in Structure                               |

|         | 4.8.2     | Changes in Technology 196                          |

|         | 4.8.3     | Preserving Capability                              |

| 4.9     | Discussi  | on 201                                             |

|         | 4.9.1     | The Technology                                     |

|         | 4.9.2     | The Organization                                   |

|         | 4.9.3     | Prospects                                          |

| CHAPTER |           | IENTIFIC RESEARCH INSTITUTE OF CONTROL             |

|         | CO        | <b>MPUTERS</b>                                     |

| 5.1     | Introduc  | tion                                               |

| 5.2     | History ( | of NIIUVM Research                                 |

|         | -         | 226 <b>Ex00 Parallel Processors</b>                |

| 5.5     |           |                                                    |

|         |           | Western Antecedents                                |

|         | 5.3.2     | The PS-2000                                        |

|         |           | 5.3.2.1 History                                    |

|         |           | 5.3.2.2 Architecture and Construction              |

|         |           | 5.3.2.3     | PS-2000 Success                                                                | 243 |

|---------|-----------|-------------|--------------------------------------------------------------------------------|-----|

|         | 5.3.3     | PS-2100     |                                                                                | 248 |

|         |           | 5.3.3.1     | History 2                                                                      | 248 |

|         |           | 5.3.3.2     | Requirements 2                                                                 | 251 |

|         |           | 5.3.3.3     | Architecture and Construction 2                                                | 254 |

|         |           | 5.3.3.4     | Performance                                                                    | 262 |

| 5.4     | A Period  | l of Change |                                                                                | 271 |

|         | 5.4.1     | Relationshi | ips with Suppliers 2                                                           | 272 |

|         | 5.4.2     | Demand fo   | r PS-2x00 Computers 2                                                          | 274 |

|         | 5.4.3     | Relationshi | ip with the Factories 2                                                        | 278 |

|         | 5.4.4     | Relationshi | ip With The Ministry 2                                                         | 283 |

| 5.5     | The Resp  | ponse to Ch | ange 2                                                                         | 284 |

|         | 5.5.1     | Changes in  | Structure                                                                      | 285 |

|         |           | 5.5.1.1     | Traditional NIIUVM Structure 2                                                 | 285 |

|         |           | 5.5.1.2     | Changes to the Structure of the Problem-oriented<br>Computing Systems Division | 287 |

|         | 5.5.2     | Changes in  | Technology 2                                                                   | 295 |

|         |           | 5.5.2.1     | The PS-2100                                                                    | 295 |

|         |           | 5.5.2.2     | The PS-2300 2                                                                  | 296 |

| 5.6     | Discussio | on          |                                                                                | 300 |

|         | 5.6.1     | The Techno  | ology                                                                          | 302 |

|         |           |             | ization                                                                        |     |

|         | 5.6.3     | Prospects   |                                                                                | 312 |

| CHAPTER | 6. TH     | E MARS P    | <b>ROJECTS</b>                                                                 | 315 |

|         |           |             |                                                                                | /10 |

| 6.1     | Introduc  | ction       |                                                                                | 315 |

| 6.2     | History   | of VTs SO A | AN SSSR Research 3                                                             | 316 |

| 6.3     | The MA    | RS Concept  | tion 3                                                                         | 319 |

| 6.4     | The Pre-  | START Ye    | ars (1983-1985)                                                                | 325 |

|         |           |             |                                                                                |     |

|         | 0.4.1     | ronnation   | of START                                                                       | )ZJ |

|         | 6.4.2     | Nature of the | he Research Plan                                 | 331   |

|---------|-----------|---------------|--------------------------------------------------|-------|

| 6.5     | The STA   | RT Years (    | (1985-1988)                                      | 333   |

|         | 6.5.1     | MARS Res      | search                                           | 333   |

|         |           | 6.5.1.1       | MARS-M                                           | 333   |

|         |           | 6.5.1.2       | MARS-T                                           | 346   |

|         | 6.5.2     | START Op      | peration                                         | 356   |

| 6.6     | The Post  | -START Y      | ears (1988-1991)                                 | 359   |

|         | 6.6.1     | Organizatio   | onal Transformation                              | 361   |

|         |           | 6.6.1.1       | Industrial START                                 | 362   |

|         |           | 6.6.1.2       | Joint Ventures                                   | 363   |

|         |           | 6.6.1.3       | Institute of Informatics Systems (ISI)           | 365   |

|         |           | 6.6.1.4       | Commerical Start                                 | 370   |

|         |           |               | Other Developments                               |       |

|         | 6.6.2     | MARS Res      | search                                           | 372   |

|         |           | 6.6.2.1       | MARS-M                                           | 372   |

|         |           | 6.6.2.2       | MARS-T/Kronos                                    | 373   |

|         |           | 6.6.2.3       | Technological Base                               | 374   |

|         | 6.6.3     | Relationshi   | ips with Industry                                | 374   |

|         |           | 6.6.3.1       | Mikroprotsessor Scientific Production Associatio | n 375 |

|         |           | 6.6.3.2       | Penza Electronic Computing Machines Factory      | 378   |

|         | 6.6.4     | Levels of S   | Support                                          | 380   |

|         |           |               | State Support                                    |       |

|         |           | 6.6.4.2       | Non-State Support                                | 381   |

| 6.7     | Discussio | on            |                                                  | 383   |

|         | 6.7.1     | The Technol   | ology                                            | 384   |

|         | 6.7.2     | The Organi    | ization                                          | 392   |

|         | 6.7.3     | Prospects .   |                                                  | 394   |

| CHAPTER |           |               | ET HIGH-PERFORMANCE COMPUTING                    | 398   |

| 7.1     | Introduc  | etion         |                                                  | 398   |

| 7.2     | Modular   | · Pipeline Pi | rocessor (MKP)                                   | . 398 |

|         |           |               |                                                  |       |

|                     | 7.2.1                                                                                                                           | MKP Architecture                                                                                                                                                                                                                                                                                                                                      |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | 7.2.2                                                                                                                           | El'brus-3-1                                                                                                                                                                                                                                                                                                                                           |

|                     | 7.2.3                                                                                                                           | MKP Development                                                                                                                                                                                                                                                                                                                                       |

| 7.3                 | Elektron                                                                                                                        | ika SSBIS ("Red Cray")                                                                                                                                                                                                                                                                                                                                |

| 7.4                 | ES-1191                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                       |

| 7.5                 | <b>Other H</b><br>413                                                                                                           | PC at the Scientific Research Institute of Control Computers                                                                                                                                                                                                                                                                                          |

|                     | 7.5.1                                                                                                                           | PS-3000                                                                                                                                                                                                                                                                                                                                               |

|                     | 7.5.2                                                                                                                           | PS-3100                                                                                                                                                                                                                                                                                                                                               |

| 7.6                 | HPC at t                                                                                                                        | he NII of Computing Systems (NIIVK) 419                                                                                                                                                                                                                                                                                                               |

|                     | 7.6.1                                                                                                                           | M-10                                                                                                                                                                                                                                                                                                                                                  |

|                     | 7.6.2                                                                                                                           | M-13                                                                                                                                                                                                                                                                                                                                                  |

|                     | 7.6.3                                                                                                                           | El'brus-M14E                                                                                                                                                                                                                                                                                                                                          |

| 7.7                 | Dynamic                                                                                                                         | e Architecture Machines                                                                                                                                                                                                                                                                                                                               |

|                     |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                       |

| 7.8                 | Macro-p                                                                                                                         | ipeline Processors                                                                                                                                                                                                                                                                                                                                    |

| 7.8<br>7.9          | Multipr                                                                                                                         | ipeline Processors                                                                                                                                                                                                                                                                                                                                    |

|                     | Multipr<br>(MCS PA                                                                                                              | ocessor Computing Systems with Programmable Architecture                                                                                                                                                                                                                                                                                              |

|                     | Multipr<br>(MCS PA<br>7.9.1                                                                                                     | ocessor Computing Systems with Programmable Architecture<br>A)                                                                                                                                                                                                                                                                                        |

|                     | Multipr<br>(MCS PA<br>7.9.1<br>7.9.2                                                                                            | ocessor Computing Systems with Programmable Architecture<br>A)                                                                                                                                                                                                                                                                                        |

|                     | Multipr<br>(MCS PA<br>7.9.1<br>7.9.2<br>7.9.3                                                                                   | ocessor Computing Systems with Programmable Architecture<br>A)                                                                                                                                                                                                                                                                                        |

|                     | Multipr<br>(MCS PA<br>7.9.1<br>7.9.2<br>7.9.3<br>7.9.4                                                                          | ocessor Computing Systems with Programmable Architecture<br>A)                                                                                                                                                                                                                                                                                        |

| 7.9                 | Multipr<br>(MCS PA<br>7.9.1<br>7.9.2<br>7.9.3<br>7.9.4<br>7.9.5                                                                 | ocessor Computing Systems with Programmable Architecture<br>(432)General Characteristics433ES-2703ES-2703 Successors437Special-purpose Systems438                                                                                                                                                                                                     |

| 7.9<br>7.10         | Multipr<br>(MCS PA<br>7.9.1<br>7.9.2<br>7.9.3<br>7.9.4<br>7.9.5<br><b>ES-270</b> 2                                              | ocessor Computing Systems with Programmable Architecture<br>(432)General Characteristics433ES-2703435ES-2703 Successors437Special-purpose Systems438Research Trends439                                                                                                                                                                                |

| 7.9<br>7.10<br>7.11 | Multipr<br>(MCS PA<br>7.9.1<br>7.9.2<br>7.9.3<br>7.9.4<br>7.9.5<br>ES-2702<br>ES-2703                                           | Occessor Computing Systems with Programmable ArchitectureA)432General Characteristics433ES-2703435ES-2703 Successors437Special-purpose Systems438Research Trends4392441                                                                                                                                                                               |

| 7.9<br>7.10<br>7.11 | Multipr<br>(MCS PA<br>7.9.1<br>7.9.2<br>7.9.3<br>7.9.4<br>7.9.5<br>ES-2702<br>ES-2702<br>Attache                                | ocessor Computing Systems with Programmable Architecture<br>(432)General Characteristics433ES-2703435ES-2703 Successors437Special-purpose Systems438Research Trends4392441                                                                                                                                                                            |

| 7.9<br>7.10<br>7.11 | Multipr<br>(MCS PA<br>7.9.1<br>7.9.2<br>7.9.3<br>7.9.3<br>7.9.4<br>7.9.5<br>ES-2702<br>ES-2702<br>ES-2703<br>Attache<br>7.12.1  | ocessor Computing Systems with Programmable Architecture<br>(432)General Characteristics433ES-2703435ES-2703 Successors437Special-purpose Systems438Research Trends43924415441d-Array Processors442                                                                                                                                                   |

| 7.9<br>7.10<br>7.11 | Multipr<br>(MCS PA<br>7.9.1<br>7.9.2<br>7.9.3<br>7.9.4<br>7.9.5<br>ES-2702<br>ES-2702<br>ES-2705<br>Attache<br>7.12.1<br>7.12.2 | ocessor Computing Systems with Programmable Architecture         A)       432         General Characteristics       433         ES-2703       435         ES-2703 Successors       437         Special-purpose Systems       438         Research Trends       439         2       441         d-Array Processors       442         ES-2335       442 |

| 7.12.5 ES-2706                                                                          | 444 |

|-----------------------------------------------------------------------------------------|-----|

| 7.12.6 Loosely-coupled Array Processor Systems                                          | 445 |

| 7.13 Special-Purpose High-Performance Computers                                         | 446 |

| CHAPTER 8. CONCLUSIONS                                                                  | 448 |

| 8.1 Introduction                                                                        | 448 |

| 8.2 The Provision of HPC Capability To the Scientific Community                         | 448 |

| 8.3 High Performance Computing in the Soviet Context                                    | 453 |

| 8.4 Technological Paradigms and Trajectories                                            | 461 |

| 8.5 The Impact of the Reform Process on Organizational Structure                        | 472 |

| 8.6 The Impact of Reform on the Development of HPC                                      | 474 |

| <ul><li>8.6.1 Economic Considerations</li><li>8.6.2 Structural Considerations</li></ul> |     |

| CHAPTER 9. WHAT IS TO BE DONE?                                                          | 484 |

| 9.1 Implications for HPC developers                                                     | 484 |

| 9.2 Implications for HPC Users                                                          | 490 |

| 9.3 Implications for Policy Makers                                                      | 495 |

| 9.4 Directions of Future Research                                                       | 497 |

| APPENDIX A. HIGH PERFORMANCE COMPUTING: CONTROLLABIN<br>AND COOPERATION                 |     |

| A.1 Introduction                                                                        | 500 |

| A.2 Controllability of High-Performance Computing Systems                               | 502 |

| A.2.1 Trends in HPC                                                                     | 503 |

| A.2.1.1 HPC Trends in the United States                    | 503 |

|------------------------------------------------------------|-----|

| A.2.1.2 HPC Trends in the Soviet Union/Russia              | 505 |

| A.2.2 Controllability of HPC                               | 507 |

| A.2.2.1 Intel Parallel Systems                             | 508 |

| A.2.2.2 Transputer-based Systems                           | 510 |

| A.2.2.3 RS/6000 Clusters                                   | 512 |

| A.2.3 Controlling the Acquisition of HPC                   | 513 |

| A.3 A Framework for Confidence-Building Measures           | 515 |

| A.3.1 Application Domains                                  | 516 |

| A.3.2 Institutional Arrangements                           | 519 |

| A.3.3 Technologies and Measures for Control and Monitoring | 522 |

| A.3.3.1 Hard Controls                                      | 523 |

| A.3.3.2 Soft Controls                                      | 524 |

| A.4 Recommendations                                        | 525 |

| APPENDIX B. GLOSSARY OF ORGANIZATIONAL ACRONYMS            | 530 |

| APPENDIX C. GLOSSARY OF ACRONYMS                           | 533 |

| REFERENCES                                                 | 535 |

## LIST OF FIGURES

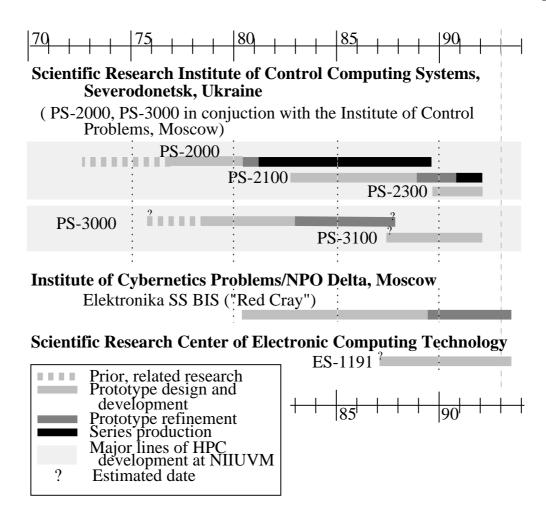

| Figure 2-1 | Conceptual Framework                                                                       | 77 |

|------------|--------------------------------------------------------------------------------------------|----|

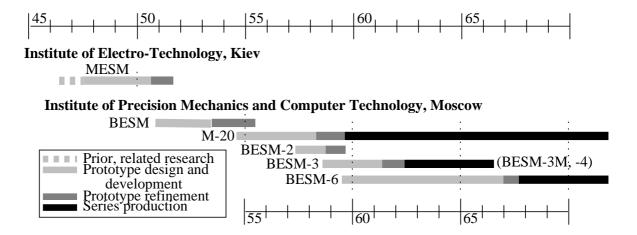

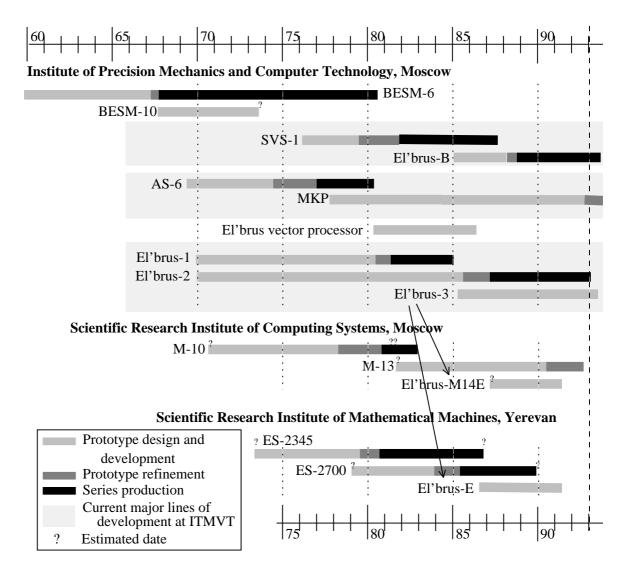

| Figure 3-1 | Early Soviet High-performance Uniprocessors                                                | 90 |

| Figure 3-2 | High-performance Computers at ITMVT and Related Institutes                                 | 97 |

| Figure 3-3 | PS- and Other Industrial High-performance Computers 1                                      | 06 |

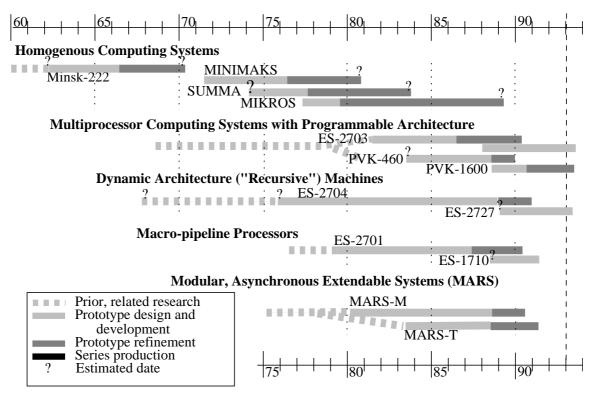

| Figure 3-4 | Academic Parallel Computing Systems 1                                                      | 10 |

| Figure 4-1 | El'brus Structure 1                                                                        | 39 |

| Figure 4-2 | El'brus-3 Structure 1                                                                      | 74 |

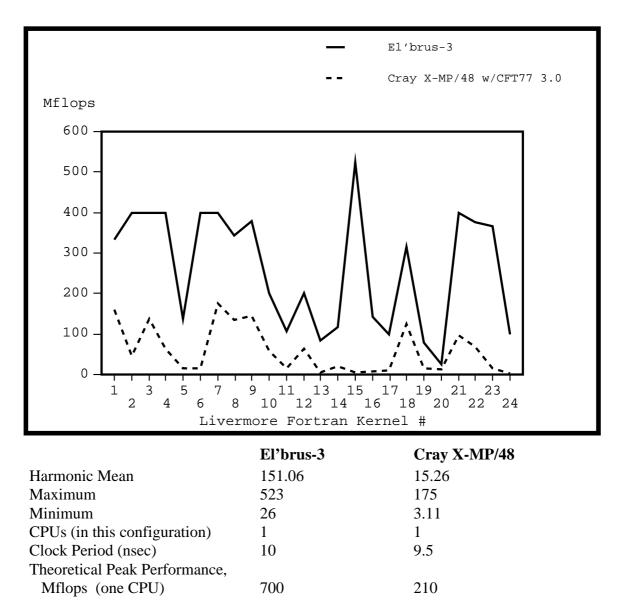

| Figure 4-3 | El'brus-3, Cray X-MP/48 Performance on LFK 1                                               | 83 |

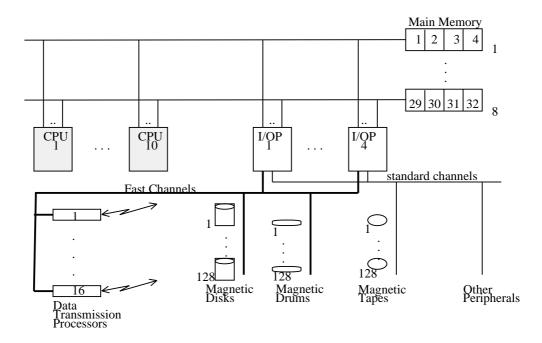

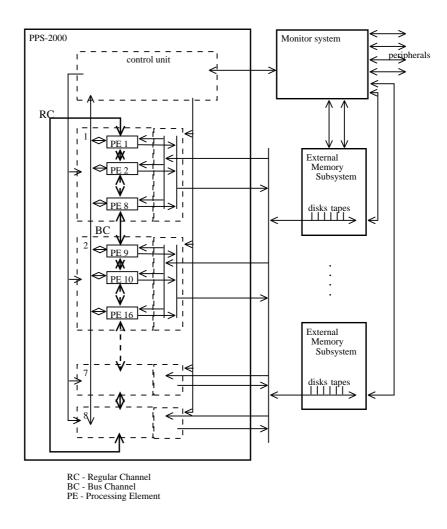

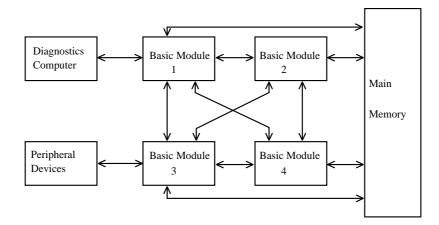

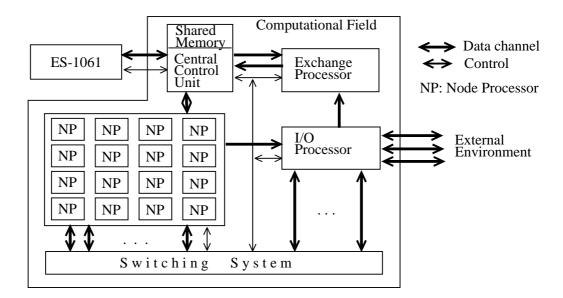

| Figure 5-1 | PS-2000 Multiprocessor                                                                     | 34 |

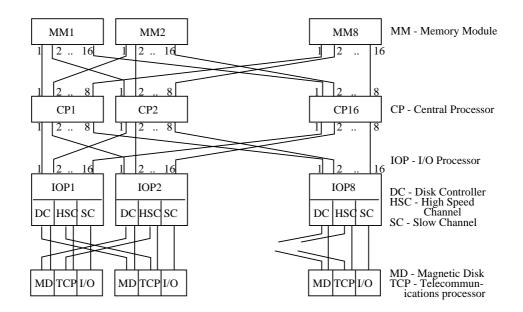

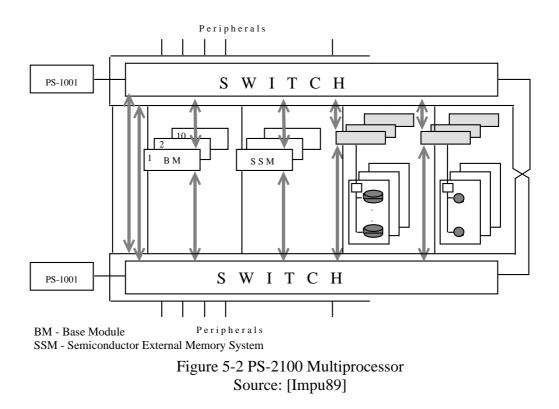

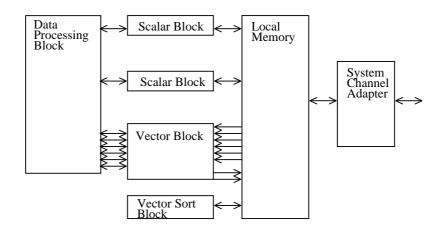

| Figure 5-2 | PS-2100 Multiprocessor                                                                     | 57 |

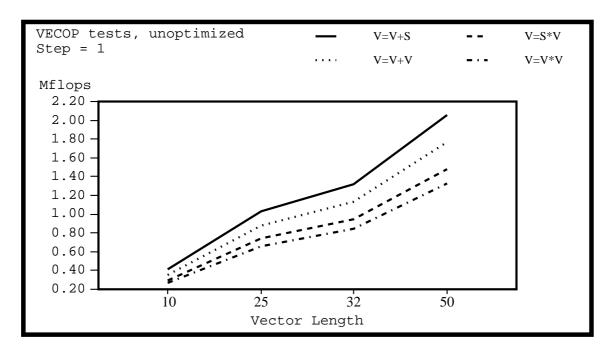

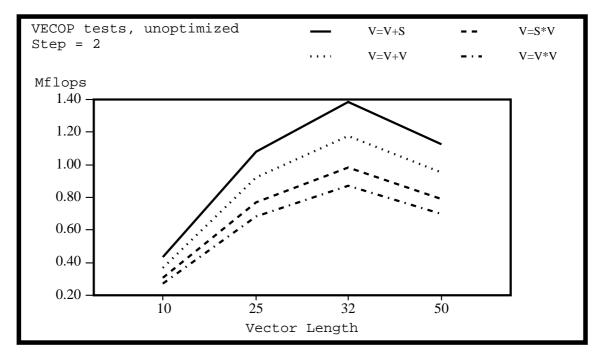

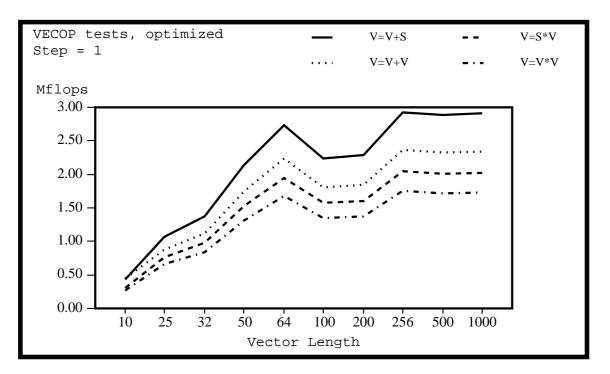

| Figure 5-3 | VECOP Results, Unoptimized, for Step = 1,2 2                                               | 67 |

| Figure 5-4 | VECOP Results, Optimized, for Step = 1                                                     | 68 |

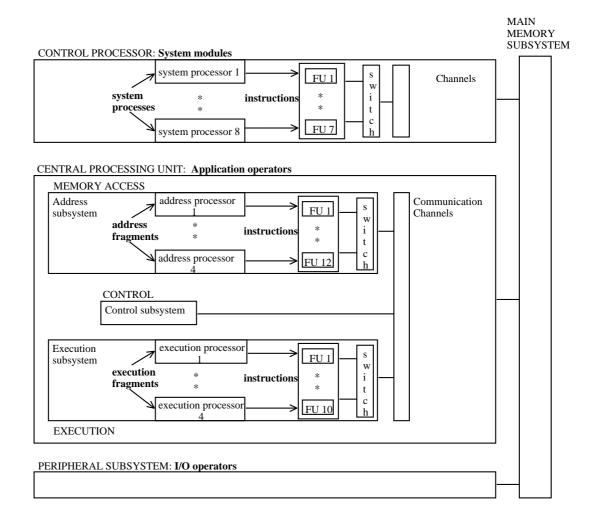

| Figure 6-1 | MARS-M Logical Structure                                                                   | 35 |

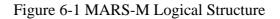

| Figure 6-2 | MARS-T Basic Module                                                                        | 47 |

| Figure 6-3 | MARS-T Logical Structure                                                                   | 48 |

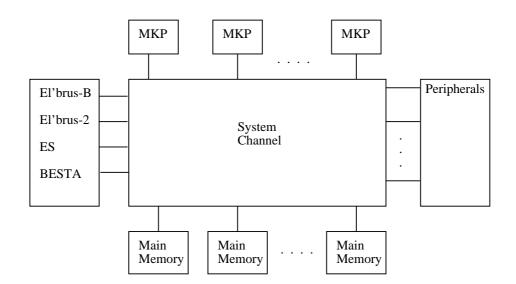

| Figure 7-1 | MKP Structure 4                                                                            | 00 |

| Figure 7-2 | El'brus-3-1 Structure                                                                      | 05 |

| Figure 7-3 | ES-2704 Structure                                                                          | 25 |

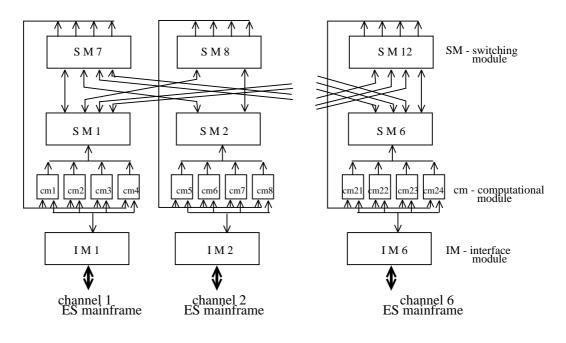

| Figure 7-4 | ES-2703 Structure                                                                          | 37 |

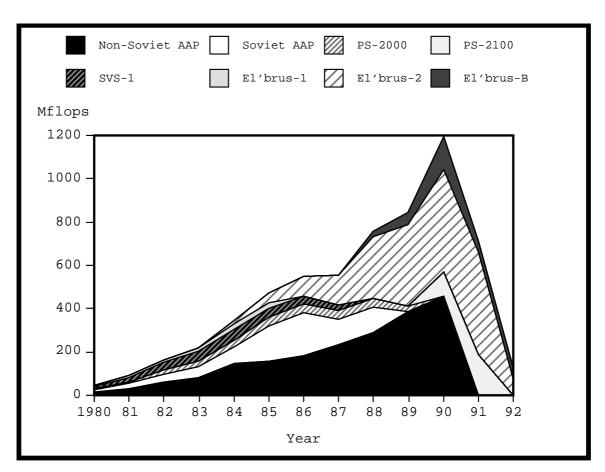

| Figure 8-1 | Annual Output of Series Produced Soviet HPC (in Mflops) 4                                  | 49 |

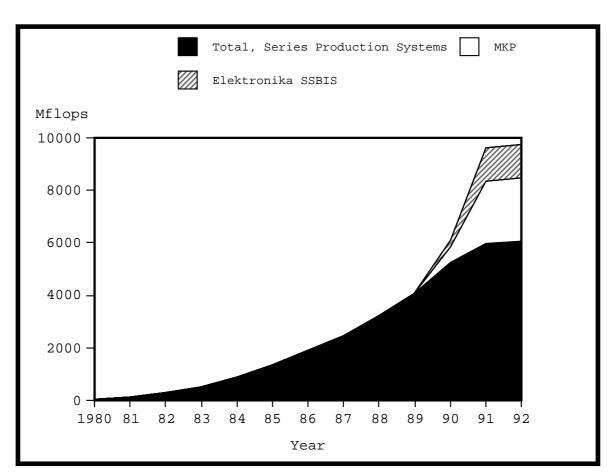

| Figure 8-2 | Cumulative Output of Soviet HPC (in Mflops) 4                                              | 50 |

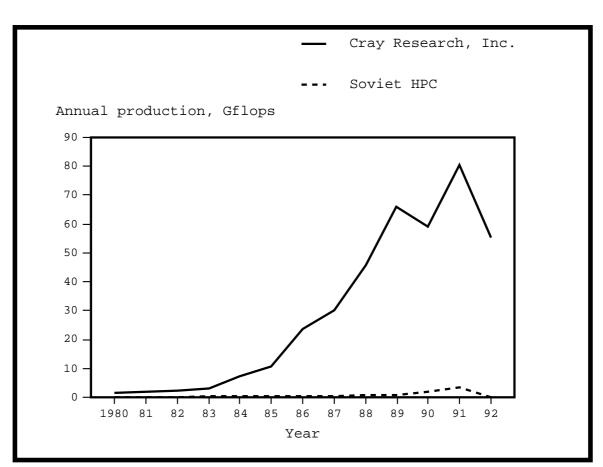

|            | Comparison of Annual Output, in Gigaflops, of Cray Research, Inc. and<br>Soviet HPC sector | 51 |

## LIST OF TABLES

| Table 3-1 | Target Characteristics of Recent El'brus Computers 102                                                    |

|-----------|-----------------------------------------------------------------------------------------------------------|

| Table 4-1 | Comparison of El'brus and B 6700 System Characteristics 138                                               |

| Table 4-2 | El'brus-2 Reliability Characteristics                                                                     |

| Table 4-3 | Factors Influencing El'brus Evolution                                                                     |

| Table 4-4 | Factors Influencing Organizational Structure within ITMVT 211                                             |

| Table 5-1 | NIIUVM Control Computers                                                                                  |

| Table 5-2 | Comparison of the PS-2100 and PS-2000                                                                     |

| Table 5-3 | PS-2100 LINPACK Results                                                                                   |

| Table 5-4 | PS-2100, Western Machines LINPACK Performance                                                             |

| Table 5-5 | PS-2100, Cray-1 Performance on Livermore FORTRAN Kernels 265                                              |

| Table 5-6 | PS-2300 Configurations                                                                                    |

| Table 5-7 | Factors Influencing PS-2x00 Evolution                                                                     |

|           | Factors Influencing Organizational Structure within NIIUVM,<br>Problem-oriented Computer Systems Division |

| Table 6-1 | MARS-M Levels and Their Features                                                                          |

| Table 6-2 | Factors Influencing MARS Projects                                                                         |

| Table 6-3 | Factors Influencing Organizational Structure Around MARS Projects 393                                     |

| Table 7-1 | MKP Functional Blocks                                                                                     |

| Table 7-2 | MKP Performance Characteristics                                                                           |

| Table 7-3 | Elektronika SSBIS Parameters                                                                              |

| Table 7-4 | PS-3000 Configurations                                                                                    |

| Table 7-5 | ES-2701 Parameters                                                                                        |

| Table 7-6 | Speed-up On ES-2703                                                                                       |

| Table 8-1 | Elements Differentiating Soviet HPC Projects                                                              |

| Table 8-2 | Spectrum of Architectural Approaches in Soviet HPC 463                                                    |

| Table A-1 | Recent U.S. High-Performance Computers 504                                                                |

| Table A-2 | Soviet/Russian High-Performance Computers                                                                 |

#### ABSTRACT

This study uses Soviet high-performance computing (HPC) as a vehicle to study technological innovation, organizational transformation, and the R&D of advanced technologies in centralized-directive economies in the past and during periods of transition. Case studies are used to identify the factors most strongly influencing the evolution of highperformance systems and the facilities within which they were developed.

Although closely tied to the military, the HPC sector was not able to overcome basic systemic and technological difficulties. HPC illustrates the limits of centralized-directive economic management's ability to coordinate and prioritize development and production of highly complex, rapidly evolving technologies. Projects were delayed by complex bureaucratic structures, the monopolistic nature of the supporting infrastructure, and resistance of production factories. Progress of individual projects was dependent on the degree to which they drove supporting industries, used immature technologies, had an industrial vs. academic orientation, and were developed in conjunction with production facilities.

The benefits of the reforms-direct contacts between organizations, increased local control of finances and research, greater flexibility in the management of R&D, and improved opportunities for international contacts-have been overshadowed by economic decline and fundamental weaknesses in the supporting infrastructure. R&D facilities have been transformed into a collection of loosely-coupled semi-autonomous organizational units, increasing short-term viability, but threatening their ability to carry out large-scale, long-term, integrated development. Links between R&D and production facilities have been disrupted. The upstream infrastructure remains ill-suited for providing the technologies necessary for HPC development. Preconditions to long-term viability are restoration of the integrity of the development-production cycle and reduction of the HPC sector's

dependency on domestic industries. Taking advantage of mass-produced Western technologies will require changes in philosophies of development and architectural approaches.

The concept of a unified sector-wide technological paradigm is not well suited for explaining the diversity of architectural approaches and specific development trajectories. A paradigm consisting of layers of "micro-paradigms" better captures the patterns of continuity and change within projects and features shared between projects.

This study suggests that the nature of the revenue stream and the opportunities for alternative organizational forms have a significant influence on organizational structure.

#### CHAPTER 1. INTRODUCTION

More than any other country, the Soviet Union was committed to science. The number of scientists per capita and the prestige they enjoyed exceeded that of any other country. Marxist-Leninist ideology viewed science and scientific methods as key to the development and management of the economy. In support of scientific advance, a huge infrastructure of educational, research and development, and production institutions was established.

Achievements in "big science" and advanced technologies in particular were used to validate the Soviet centralized directive form of management of science and the economy in the eyes of the domestic population and the international community. Soviet scientists and policy-makers frequently boasted of the advantages of such a system in marshaling huge resources and focusing them on priority programs such as space exploration, nuclear power, military systems, oil and gas development, computing and others.

Advanced technologies are characterized by their complexity in design and/or manufacture, and a rapid evolution which often establishes the state-of-the-art in the field. Their development depends on a vast infrastructure of supporting industries. Thanks to national security concerns and controls in both the Soviet Union and the Western members of the Coordinating Committee for Multilateral Export Controls (CoCom),<sup>1</sup> complete infrastructures for advanced technologies with military applications in the Soviet Union had to be developed independently of the corresponding Western industries, even when those technologies—so-called dual use technologies like computers—had significant and widespread civilian applications.

<sup>&</sup>lt;sup>1</sup>CoCom includes Japan and all the member nations of the North Atlantic Treaty Organization (NATO) except Iceland.

In spite of some successes, Soviet achievements in advanced technologies and science more generally have lagged behind those of the West when measured by the level and quantity of results, number of Nobel Prizes earned, etc. From the 1960s through the mid 1980s, the Soviet economy as a whole "stagnated," experiencing declining growth rates and growing inefficiencies, and an increasing technological lag behind the Western capitalist countries. Against this backdrop, Mikhail Gorbachev launched a program of economic restructuring (*perestroika*) in 1985 in an effort to revitalize the USSR economy. Above all, the economy was to be reformed through the acceleration of scientific and technical progress in a new stage of the scientific-technical revolution (NTR). This stage was to be characterized by accelerated development and assimilation of new technologies, including advances in microelectronics and computing, computer-aided manufacturing, materials, etc. in an effort to increase the output and efficiency of the economy without dramatically increasing inputs.

In the eight years since the start of *perestroika*, the Soviet Union and its successor states have experienced profound economic, political, and social change far exceeding the intentions of Gorbachev and other leaders. Indicators such as the rapidly falling gross domestic product, crime rates, and runaway inflation paint a picture of catastrophe. However, such indicators do not help us understand the underlying phenomena and processes which have led to these results. They do little to help us understand the degree to which, within the chaos, the foundation is being laid (or not being laid) for the future rejuvenation of the economies of the former Soviet republics and, in particular, their scientific and technical base. To understand these transformations one must look not only at macro-level indicators, but also at the processes at work at the micro-level–in individual technologies, research teams and institutes, and within various branches of the economy.

In this study we seek to contribute to an understanding of the development and transformation of Soviet advanced technologies and their organizational and environmental context, both prior to *perestroika* and during the reform period from 1985 through December, 1992, approximately one year after the dissolution of the Soviet Union. Our vehicle will be a detailed examination of research and development (R&D) facilities and projects within the Soviet high-performance computing (HPC) sector. We wish to document the development of HPC systems within these organizations, identify the factors which have shaped their development, and analyze the impact of the social, political, economic and technical changes since 1985 on these technologies and the organizations within which they have been carried out. Through such an analysis, we hope to cast light on the prospects for HPC in particular, and advanced technologies more generally in the Soviet Union's successor states.

Since the dissolution of the Soviet Union in December, 1991, terminology has become particularly problematic. The Soviet Union has been replaced as a political entity by fifteen independent countries, some of which have formed a loose confederation called the Commonwealth of Independent States. All of them have sought to distance themselves from the Communist legacy and have removed the words "Soviet" and frequently "socialist" from official names. At the same time, it is impossible for any of these states or the organizations and people within them to wipe the slate of history clean. They are bound to and influenced by their history in the Soviet Union. They share many problems, features, and trends precisely because they once were part of the Soviet Union. For this reason, we will use the terms "Soviet" and "Soviets" to refer to institutions and individuals which had their origins in the Soviet Union and which still exhibit the influence of the Soviet economic, political, technological, and social systems, even when we refer to events after the Soviet Union's breakup. We will refer to the Soviet Union's successor states as "Soviet states," and the republics of the Soviet Union as "Soviet republics." Only when the distinction is important will we use "Russian," "Ukrainian," etc. We are also likely to use the latter when refering to institutions which originated (rather than metamorphised) after December, 1991 and are closely associated with one particular state.

High-performance computing provides an excellent vehicle for studying advanced technology in the Soviet Union and its successor states because of the nature of the technology itself, the nature of the infrastructure which supports this sector, and the importance of this particular technology to many critical spheres of activity in the military and civilian sectors, and its geo-political implications. Its study can cast light on a broad spectrum of issues, from technological innovation, organizational transformation, the Soviet reform process, the conduct of research and development, military and economic competitiveness, technology transfer of dual-use technologies and export control policies, and others.

High-performance computing represents one of the Soviets' "best shots" in computing. In a tradition stretching back to Lenin, Soviet leaders have viewed technological advance as a key to economic development. The acceleration of scientific-technical progress and the wide-spread introduction of new generations of technologies was proclaimed a "key lever in the intensification of the national economy" [Vasi88]. They were a prominent feature of the ambitious international Comprehensive Program for Scientific-Technical Progress of the CMEA<sup>2</sup> Countries to the Year 2000 (Program to the Year 2000). In this program and for many year prior, high performance computing has

<sup>&</sup>lt;sup>2</sup> The Council for Mutual Economic Assistance (CMEA) included members of the Warsaw Pact plus Cuba, Mongolia, and Viet Nam. The latter three played an insignificant role in CMEA computing. Those having the greatest impact on computing in the Eastern Bloc were Bulgaria, Czechoslovakia, the German Democratic Republic, Hungary, Poland, and the USSR.

been a high-profile, high-priority advanced technology. Not only are powerful computers tools to be used in scientific, economic, and military activity. They are symbols, often viewed as indicators of a nation's technological capability. The Soviet high-performance computing sector has drawn considerable financial, material, and human resources over many years. Because it has been one of the most innovative sectors of Soviet computing, providing rich research opportunities, high-performance computing has attracted some of the leading computer scientists and engineers in the country. A study of Soviet high-performance computing can shed light on what Soviet science has been capable of in a very important field.

High-performance computers are highly complex systems. They typically consist of thousands of components and subsystems, each of which can be considered a system with hundreds or thousands of elements. Hardware is highly complex, but does not reflect the full extent of a system's complexity. Basic hardware units such as gate arrays are altered to reflect a highly complex logical design. Software can be even more complex, since software designers tend to avoid duplicating code which serves the same, or similar functions. Computers are highly dependent on miniaturization. The ability to place thousands, or even millions of transistors on a single chip measuring only a centimeter or two on a side requires complex, high-precision manufacturing tools and extraordinarily pure input materials and processing conditions; such components cannot be created manually by skilled craftsmen with "golden fingers." As a result, computers have greater complexity per unit volume than any other device created by man. Through a study of these systems, we can identify strengths and weaknesses of the Soviets' ability to design, construct, and manufacture complex technologies.

The final product is dependent on a long chain of activities and products such as fundamental research, applied research, materials production, component and subsystem development, machine architecture design, unit assembly, design and production technologies, and systems support services. Weaknesses in any link of the infrastructure can have serious consequences in the final product. Because HPC systems and their infrastructure are so dependent on each other, an examination of the end products can cast much light on the nature of the infrastructure and the changes that it might be undergoing. HPC systems can contribute much to our understanding of Soviets' ability to develop and manufacture advanced technologies with are also complex and highly sensitive to a wide range of inputs and upstream products and processes, both prior to 1985 and after. The study of high-performance computers is futher important because they not only are an output of this infrastructure, but also help shape its nature. They are critical tools for the development of next generation systems and components, and in both the East and the West traditionally have been among the most advanced systems, creating demands which have caused the entire infrastructure to raise its technological level.

The Soviet high-performance computing sector is inter-administrative. To a greater degree than other parts of the computing and electronics sectors, high-performance computing involves the participation of a range of administrative entities. Nearly all projects include significant research at Academy of Sciences or VUZ (Institutions of Higher Education) institutes. Research, development, and production were carried out in industrial ministries such as the Ministry of the Radio Industry and the Ministry of Instrument-Building, Means of Automation, and Control Systems (Minpribor). Inputs such as integrated circuits, materials, and selected subsystems come from other ministries. The military also has played a significant role as a key customer and project sponsor. Decisions about HPC involved policy makers at the highest levels of the Academy of Sciences, branch ministries, the USSR Council of Ministers, state agencies, and the Military-Industrial Commission (VPK). Successful HPC development required the coordination

and cooperation of multiple administrative entities. As a result, Soviet high-performance computing provides a lens into basic decision making from the highest levels of government down, R&D processes within many industrial and academic branches of the economy, and the nature of the relationships between them. HPC is therefore also a useful vehicle for examining the changing roles of these organizations and their interaction.

High-performance computers are important enabling technologies in many areas of science and industry. Increasingly, supercomputers are becoming an essential tool in the development of advanced technologies in aerospace, computing, weapons design, materials and others. These industries rely on supercomputers for design, analysis, simulation, and visualization to improve product quality and functionality, shorten development cycles, and reduce labor and material costs. Computational methods have emerged as a third pillar of scientific advance, together with analytical and experimental methods. Numerical analysis and visualization have emerged as basic tools in a growing number of fields such as weather prediction, hydrodynamics, plasma physics, atomic and molecular structure, etc. If the Soviet states are to be broadly competitive internationally in these and other disciplines, their researchers and engineers must have access to high-performance computing systems.

High-performance computers are also useful for examining geo-political aspects of advanced technology. HPC systems are an excellent example of a dual use technology with broad applicability to both military and civilian applications. Few dual use technologies have been as consistently and tightly controlled by the CoCom nations as HPC. At the same time, HPC underscores the issues and difficulties surrounding export control regimes during the post-Cold War era. Thanks to rapid technological developments, high-performance technologies are becoming much more difficult to control. Western high-end supercomputers, still manufactured in small quantities and requiring considerable on-site support, remain relatively controllable. Advances have been so rapid, however, that today's workstations and mid-range systems offer functionality and performance available only on supercomputers a decade ago. These systems are often manufactured in large, uncontrollable quantities (100,000 or more) and are small enough that transporting them is trivial. Leading-edge technologies move into the commercial mainstream only a few years after introduction, and many Western massively parallel highperformance computers contain a very high percentage of off-the-shelf parts. At the same time, the relationship between the West and the Soviet states has become much less adversarial, but the latter's future stability and sensitivity to the former's national security concerns are by no means assured. These factors are forcing a reconsideration of Western and Russian export control policies [Nrc93].

Because the Soviet high-performance computers have for decades been developed independently of the West in a rather closed sector with limited transfer of technology from outside the Soviet Union, they provide a microcosm in which to study issues of technological innovation and the nature of technological advance within a specific set of social, economic, and political systems. Prior to the *perestroika* reforms, these systems were rather stable. Since 1985, they have experienced drastic changes, and the isolation of this sector from the West has eased considerably. Under these conditions, Soviet HPC technologies should help us learn more about technological innovation during highly dynamic periods which create drastically new opportunities and constraints.

Similarly, Soviet HPC provides a microcosm in which to study organizational development and transformation under changing conditions. Traditionally, organizational structures in the Soviet Union were very stable and given types of organizations throughout the country had very similar structures. The reforms have created great pressures on organizations and radically new opportunities for transformation. Besides the reasons mentioned above, the Soviet HPC sector provides a useful vehicle for studying these issues because it is relatively small. It is possible to study nearly all the major projects and R&D centers in the entire sector. In doing so, we avoid many of the methodological problems associated with selecting a study sample and generalizing to the entire sector.

We will investigate HPC-related activities within one component of the Soviet highperformance computing sector-research and development facilities in industry, the Academy of Sciences, and the institutions of higher learning (VUZ). As pointed out in [Meye90], a study of the activities of individual firms should not be equated with the study of an industry or industrial sector as a whole. But a study of research and development facilities and their products provides an important piece of the over-all picture. R&D facilities are crucial to the health of advanced technology industrial sectors. In them the ideas, abstractions, and theorizing meet the realities of the physical world. Innovation is strongly shaped by not only the theoretical ideas generated, but also the opportunities and constraints imposed upon the process by a host of material, technical, social, and political factors. The results of R&D strongly affect the quality, performance, and innovativeness of products manufactured within an industrial sector. While improvements in R&D do not necessarily lead to improvements in the output of an industrial sector as a whole, a deterioration within R&D facilities will almost certainly have a negative impact on the sector's output. R&D facilities are also a critical point of interaction between sponsors, planners, developers, manufacturers, and users. While this study focuses on HPC R&D facilities and the technologies developed within them, we will necessarily touch on these other elements as well.

In chapter 2 we discuss several bodies of related research and the contribution a study of Soviet HPC can make to each. We also present the specific research questions and the case study methodology used to address them. Chapter 3 gives an overview of the HPC sector. We present some of the sector's history, and place the numerous industrial and academic systems in the context of the sector as a whole. This sets the stage for three detailed case studies, covered in chapters 4, 5, and 6. Chapter 7 contains sections that discuss HPC projects (or sets of projects) not covered in the detailed studies. This chapter ''rounds out the field,'' making our study quite comprehensive in its coverage. It also illustrates that the processes at work in projects discussed in earlier chapters are not unique, but apply more broadly throughout the sector. Chapter 8 provides a cross-cutting analysis of the individual projects and conclusions drawn from this study. In chapter 9, we discuss the implications of our study for Soviet HPC developers and users, and Western and Russian policy-makers, and suggest directions for future research.

#### CHAPTER 2. RELATED RESEARCH AND METHODOLOGY

Our study extends four areas of research: innovation in the Soviet Union, computing in the Soviet Union, Western research on innovation, and organizational development. In this chapter we discuss the literature in these areas, the research questions, the research methodology and the conceptual framework which serves as a platform for the study.

#### 2.1 Technological Innovation in the Soviet Union

#### 2.1.1 Characteristics of Soviet Science

Loren Graham has commented that the Soviet Union was "a nation with an explicit commitment to science, including a value system and a philosophical world view based on science, which is unmatched in intensity by any other nation in the world" [Grah75, 12]. Although Soviet thinking about the role of science in society and the drive towards a communist society has varied since the inception of the Soviet state, it has always figured prominantly. During the 1960s science was given enhanced status when it was declared a direct productive force in its own right, on a par with production, rather than something which lagged behind, and was subordinate to, production. The post-Stalin years saw a rapid increase in the number of researchers and research facilities. Statistics on the number of research personnel are difficult to obtain, interpret, and compare, but many who have examined this question have concluded that the USSR had considerably more people working in research than any Western country, both overall and as a percentage of the working population [Fort90, 8]. High-ranking scientists have enjoyed considerable prestige and benefits in the Soviet society. Science as a whole has been rather well funded for many decades under Soviet rule.

Nevertheless, the Soviet Union trails the United States in many common indicators of scientific performance: number of Nobel Prizes, origin of major breakthroughs, fre-

quency of citation by fellow specialists [Gust80, 31]. Both Western and Soviet writers have for many years been critical of the Soviet Union's inability, with some exceptions, to generate world-class research results and innovations, and see the latter through into production and use within the national economy, particularly from the 1960s to the present. (See [Fort90; Nolt88] for references to this literature.)

A number of researchers have identified some of the general features of Soviet science. Thane Gustafson describes five dominant charateristics: 1) Soviet pure science is strongest in fields that depend the least on material support (instrumentation, sophisticated materials, and equipment); 2) Soviet science is often slow to accept radical conceptual changes or take up new approaches; 3) in several fields, Soviet scientists have achieved results through long-term efforts in traditional specialties and established methodologies; 4) when they do make crucial breakthroughs, Soviet scientists are often unable to maintain their lead; 5) Soviet science holds leading positions in fields that enjoy highlevel attention [Gust80, 32-33]. Others focusing more on applied research point out the long implementation cycles, weak links between science and production, the reluctance of industry to use the results of science, the relative isolation of the Soviet scientific community from its Western counterparts [Fort90].

#### 2.1.2 Analyses of Innovation in the Soviet Union

Western and Soviet scholars have identified numerous factors which have contributed to the state of Soviet science and its ability to produce quality, useful results. Joseph Berliner's study on the decision to innovate in Soviet enterprises was the first in-depth look at the question of innovation in the Soviet context [Berl76]. Berliner does not attempt to explain fully the rate of innovation throughout the entire economy, or the genesis of innovation itself. Rather, he focuses on the civilian industrial sector and deals with the factors which affect the assimilation of new products and processes into production, rather than those that impact the earlier stages of technological process [Berl76, 3]. Neither does he address questions of economic and science policy, the technical characteristics of society such as tastes and values which influence demand, or historical or cultural influences. The four structural properties of the economy which he examines are prices, rules which guide decision makers, incentives, and the organizational structure of the economic system as a whole [Berl76, 12]. Organizational structure includes both the units that comprise the system and the ways in which they relate to one another [Berl76, 29].

In a series of two volumes [Aman77; Aman82], Amann and Cooper have assembled a number of case studies examining the technological level of various branches of industry and technological innovation within the Soviet Union. These volumes have tried to provide a greater level of detail about the technological level of Soviet industry, and address what they feel is a weakness of the general surveys—their tendency to present general patterns which reveal little of the patterns of variation between industries, and their emphasis on national policy and planning or on the individual enterprises with little exploration of the intermediate relationships between the ministries and their subordinate research and development institutes [Aman82, 8].

The Berliner and Amann and Cooper studies complement each other, and provide a solid view of technological innovation under the pre-*perestroika* system. Much has changed since 1985, however, and a goal of our research is to examine how the process of technological innovation has changed, within one sector. [Aman82] and [Berl76] suggest that given the changes observed in the Soviet Union, one might reasonably expect to see significant change in the process of technological innovation. In his introduction, Amann comments that "[a]bsence of competition and user feedback represents perhaps the most potent single factor inhibiting the pace and scope of innovation in the USSR" [Aman82, 12,254]. Berliner suggests that "[a]ny structural reforms designed to acceler-

ate the rate of innovation must therefore alter the traditional balance of reward and risk....The appropriate alteration of the balance of risk may be accomplished by a structural change designed to increase the degree of enterprise autonomy over its transactions with other enterprises and organizations'' [Berl76, 522]. Hage calls the amount and variety of strategic decisions made by members of the organization organizational autonomy and regards it as a significant variable [Hage80, 387]. As we shall see below, the reforms have introduced greater levels of competition, feedback from users, and local autonomy. Are these changes bringing about the improvements in innovation predicted by Berliner, and Amann and Cooper?

Other researchers have examined innovation as part of a broader look at scientific research and development as a whole, within the Soviet context. Many features of science more generally and technological innovation in particular are directly or indirectly related to the centralized nature of the management of the economy. While it is generally not the case that science projects are determined in a "top-down" fashion with individual scientists having little input in the planning process [Fort86], the Soviet system was characterized by vertical administrative controls which strongly affected the allocation of resources, the inter-organizational coordination, and the indicators and incentives which shape R&D and production. Bruce Parrott describes some of the administrative rigidity of the management of science even during the 1960s and 1970s when efforts were being made to decentralize somewhat the highly centralized system inherited from Stalin [Parr80, 75]:

> Administratively, all changes in the internal structure of individual scientific research bodies continued to require the consideration and approval of their ministerial overseers. Financially, research units were asked to submit highly detailed annual budgets, and once these estimates were approved, transfers among budgetary categories on the units' own authority were not permitted. In addition, these estab

lishments depended on centralized material-technical supply; they could not, without higher approval, sell or trade equipment that was no longer useful to them. Finally, in selecting research topics, each unit had to submit for the confirmation of its superior ministry or department a thematic research plan that specified most of the research to be undertaken in the coming year.

Besides limiting a research institute's ability to respond in a flexible manner to changing research conditions or advances in the field, such an arrangement can greatly increase the length of research cycles. Needs must be specified months or years in advance with little guarantee that they will be fulfilled. It is difficult under these circumstances to make changes-to acquire unanticipated supplies or equipment-in the middle of a plan period [Gust80, 52].